# Caratteristiche Area/Ritardo

Maurizio Palesi

#### Motivazioni

- L'ottimizzazione di un circuito comporta normalmente un compromesso tra

- Prestazioni (ritardo di propagazione)

- → Area (o costo)

- → Potenza dissipata

- → Testabilità

- **→**...

#### Ottimizzazione Logica a Due Livelli

- Faremo riferimento all'ottimizzazione logica a 2 livelli (somma di prodotti o prodotti di somme)

- → Ha un impatto diretto sul progetto di macrocelle basate su PLA

- Rappresentano le componenti fondamentali delle logiche multi-livello

- Rappresenta un modo formale per elaborare la rappresentazione di sistemi che possono essere descritti mediante funzioni logiche

### Copertura

- La copertura di una funzione Booleana è l'insieme degli implicanti che coprono tutti i mintermini

- La copertura minima è la copertura di minima cardinalità

- Non è detto che la copertura minima sia quella a minore costo

- Dipende dallo stile di implementazione

- ✓ PLA: riduzione dei termini prodotto e poi riduzione dei letterali

- ✓ Complex Gates: più sensibile alla riduzione dei letterali

- L'obiettivo dell'ottimizzazione logica a due livelli è quello di determinare la copertura minima

#### Risultati Ottenibili

- Circuiti a 2 livelli e 1 uscita

- Metodo esatto per identificare gli implicanti primi essenziali (mappe di Karnaugh)

- Metodo esatto o approssimato per identificare una copertura ottima (metodo di Quine-McCluskey)

#### Risultati Ottenibili

- Circuiti a 2 livelli e più uscite

- Metodo approssimato per trovare una copertura ottima (identificazione esatta degli implicanti essenziali di ogni singola uscita)

- Ottimizzazione congiunta per sfruttare i termini prodotto condivisi

#### Risultati Ottenibili

- Circuiti multilivello a una o più uscite

- Numerosi metodi approssimati per esplorare le diverse alternative area/ritardo

- Sintesi ottima a due livelli di porzioni del circuito

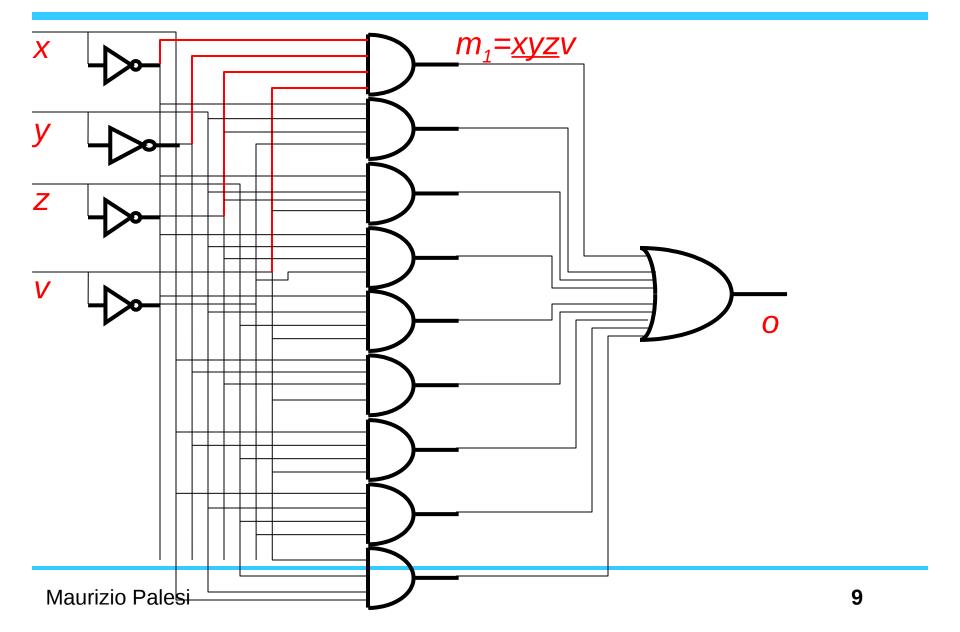

- Per le realizzazioni a due livelli (somma di prodotti o prodotti di somme) è chiara

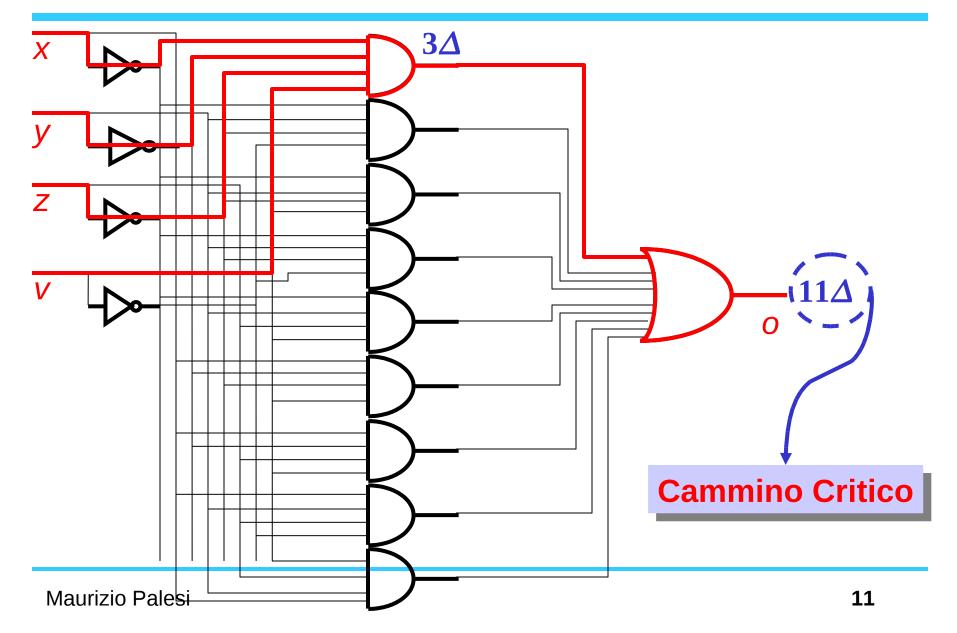

- **Esempio**:

o =

$$f(x,y,z,v)$$

=

{ $m_1,m_4,m_5,m_6,m_7,m_9,m_{11},m_{14},m_{15}$ }

## Relazione tra Area e Ritardo (Ottimizzazione dell'Area)

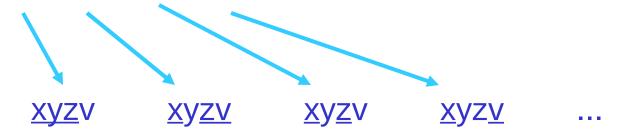

Si considerino i mintermini:

- $\rightarrow m_4 = \underline{x} \underline{y} \underline{z} \underline{v}$

- $\rightarrow m_5 = \underline{x} \underline{y} \underline{z} \underline{v}$

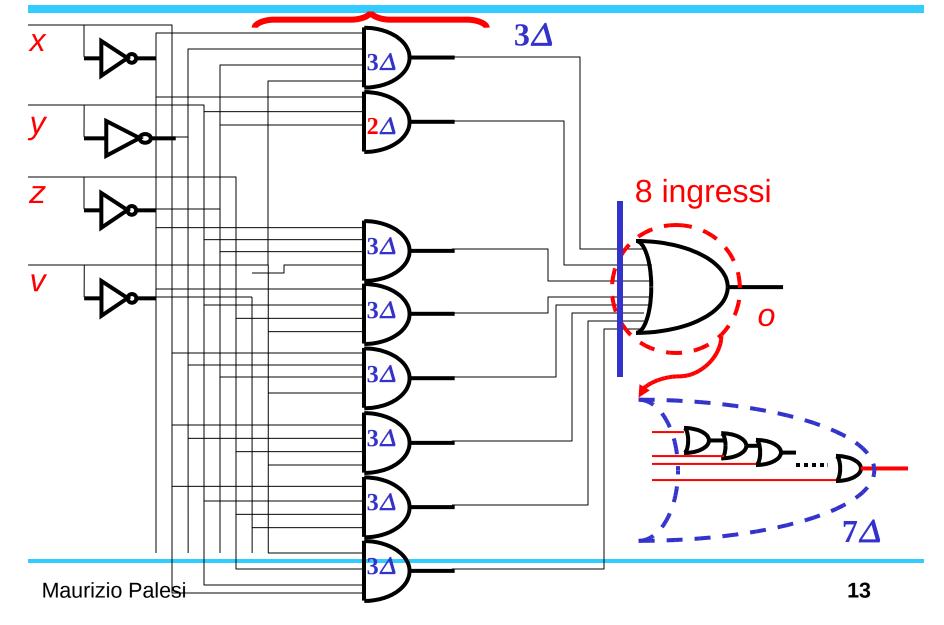

- Due prodotti (2 porte AND a 4 ingressi)

- Però possiamo:

- $\rightarrow \underline{x}\underline{y}\underline{z}\underline{v} + \underline{x}\underline{y}\underline{z}\underline{v} = \underline{x}\underline{y}\underline{z}(\underline{v} + v) = \underline{x}\underline{y}\underline{z}$

- Un prodotto (1 porta AND a 3 ingressi)

- ✓ Ottimizzazione in area (1 porta in meno)

- ✓ Nessuna ottimizzazione in ritardo per il primo livello (i restanti mintermini contengono tutti i letterali)

- →Inoltre la porta OR diventa a 8 ingressi

- $\checkmark$  Ottimizzazione in rirardo nel secondo livello ( $7\Delta$ )

## Relazione tra Area e Ritardo (Ottimizzazione dell'Area)

## Riepilogo

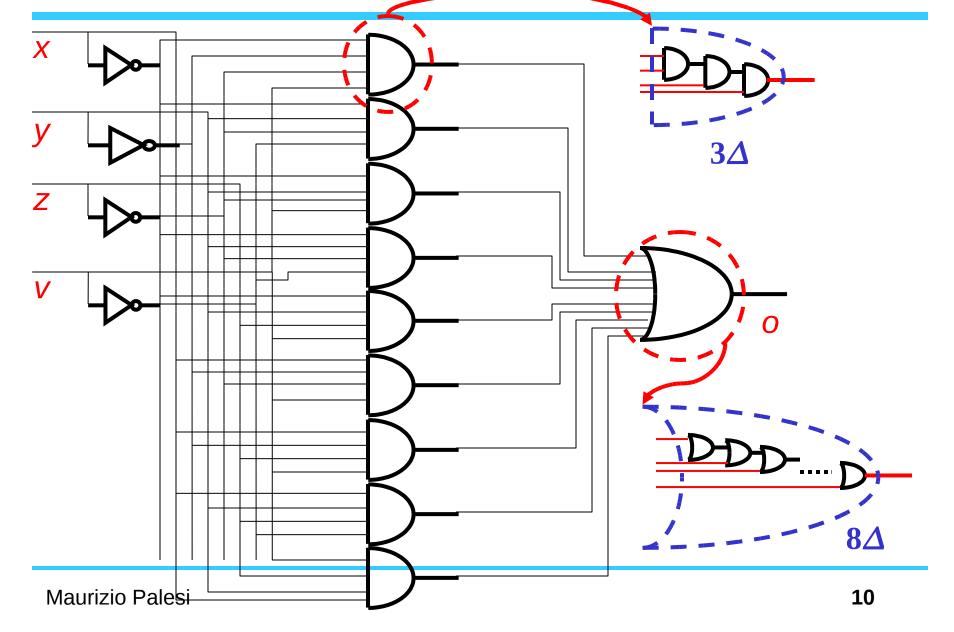

- In un circuito a due livelli (somma di prodotti)

- → La riduzione del numero di prodotti riduce sia l'area che il ritardo

- Eliminazione di un letterale

- ✓ Riduce il numero di ingressi nella porta AND (riduzione di area)

- ✓ Riduce il ritardo di un solo segnale che arriva agli ingressi della OR ma non è detto che riduca il ritardo del cammino critico

#### Ottimizzazione

- L'ottimizzazione dei circuiti a due livelli segue quindi il criterio molto semplice di identificare la copertura minima

- Alla copertura minima corrisponde il circuito a due livelli di area minima e ritardo minimo

#### Note

- I circuiti a due livelli sono difficilmente realizzabili dal punto di vista tecnologico

- ✓ Area e velocità inadatte per circuiti di grosse dimensioni

- ✓ Si usano invece circuiti multilivello per i quali la struttura non è nota a priori ma è il risultato del processo di ottimizzazione

#### Ottimizzazione

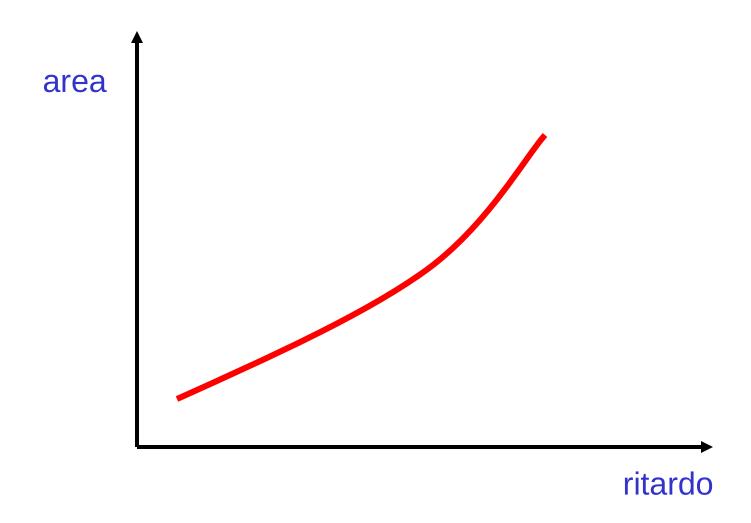

- Gli obiettivi dell'ottimizzazione logica a due livelli e multi-livello sono differenti

- →Per logica a due livelli rappresentata come somma di prodotti

- ✓ Area e ritardo sono proporzionali alla dimensione della copertura

- ✓ Ottenere una copertura minima corrisponde ad ottimizzare sia area sia in ritardo

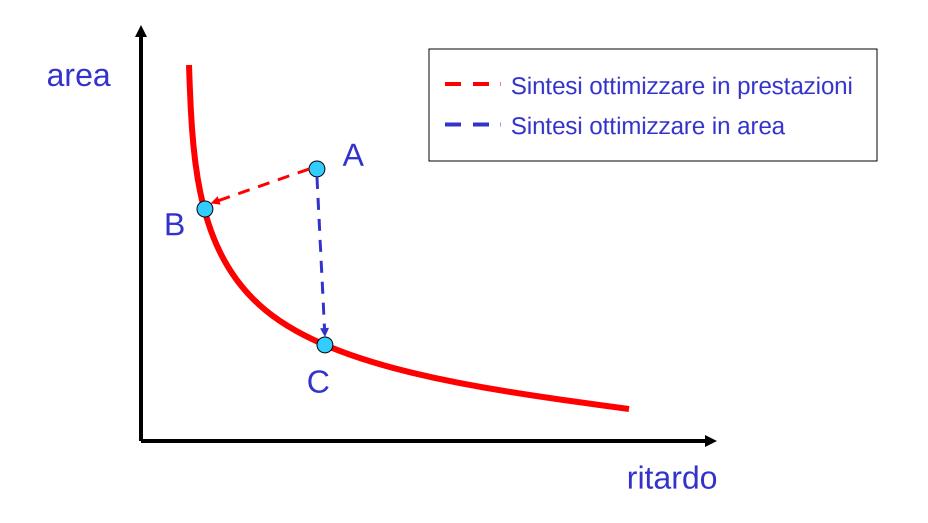

- →Per logica multi-livello

- ✓ Implementazione ad area minima non corrisponde a implementazione a ritardo minimo e viceversa (es. addizionatori)

- ✓ Compromesso tra area e ritardo

#### Ottimizzazione Area/Ritardo

Logica a 2 Livelli

#### Ottimizzazione Area/Ritardo

Logica Multi-livello